What does this mean for us?

Further upsides to DDR4 include less motherboard space wasted on ugly memory slots, but obviously the downside is less upgrade potential without replacing your entire set of memory.Although before we throw our hands in the air in disgust at another upgradable privilege lost, is it really that big a deal? Big jumps in memory needs take years to transition from “nice to have” to “now useful” to “absolutely needed”, so replacing your PC memory with more capacity will likely co-incide with a frequency and performance bump too.

4GB kits have been available for a long while and are firmly in the "now useful" area, and are well on the way to "absolutely needed". 8GB kits (comprising two 4GB DIMMs) are now hitting the mainstream market and combined with the recent move to lower 1.35V for select ICs, there's double the reason to upgrade.

Adding another 4GB to 4GB already in your system is still cheaper than rebuying memory (if you already own a DDR3 system) - but DDR4 has another trick up its sleeve: a new IC stacking technology called TSV that should offer a greater variety of capacities from the get-go than we've ever seen before.

Stack them chips! Nom-Nom-Nom

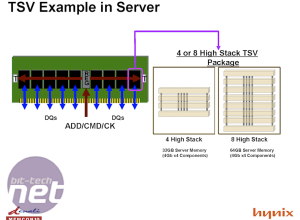

Through-silicon Via, or TSV, has been mulled by Intel at its IDF conferences for several years already, as a method of stacking many - possibly tens to hundreds of - CPU cores directly to large quantities of memory.

The technique is being highlighted as a way to increase memory capacity for DDR4 systems, where ICs will be stacked up to eight high. Each die has gaps that allow vertical electrical pillars to shoot through in order for the signal to reach the electrodes at the base.

This beats the old, expensive and fragile method of soldering very teeny copper or gold wires to the edges of each IC (wire bonding). Other direct advantages include lower power and less voltage drop, due to shorter trace lengths and a much greater potential density of I/O.

However there are other design issues to address like heat density, cooling and voltage requirements for many transistor dense dies stacked together. These are challenges dense 3D IC making has not previously considered with 2D design and simple chip stacking and could well affect reliability. Adding more dies to an IC surely only increases the risk of one limiting the potential overclock, although that argument is no different from adding two additional DIMMs with a total of 32 extra ICs into a dual channel DDR3 system.

The big questions remain to be answered then: is it a consumer (cost) friendly process and how well does TSV cope with overclocking? We'll have to wait for the first samples in 2011-12 to find out.

MSI MPG Velox 100R Chassis Review

October 14 2021 | 15:04

Want to comment? Please log in.